[lwptoc]

Einleitung

Die Entwicklung von Funktionen für einen FPGA sind einerseits vergleichbar mit der Entwicklung von Software, andererseits auch vergleichbar mit der Entwicklung von Hardware. Es ist eine Mischung aus beiden Welten, so dass eine Spezialisierung erforderlich ist.

Nachfolgend stelle ich verschiedene Themen aus dem Bereich VHDL und FPGA vor, die mich schon begleitet haben.

Rund um die FPGAs

Was macht ein FPGA, welche Unterlagen gibt es und welche Funktionen lassen sich implementieren?

Die ein weitere Fragen beantworten die folgenden Abschnitte.

Die 6 wichtigsten Userguides für Xilinx Spartan 6

Es gibt eine Menge Userguides für die verschiedenen FPGAs von Xilinx. Im folgenden gehe ich auf die 6 wichtigsten Userguides für die Xilinx Spartan 6 FPGAs ein.

SelectIO Resources User Guide

UG381 – Spartan-6 FPGA SelectIO Resources User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Charakteristik und technische Werte der Ein- und Ausgänge

- Beschreibung der verschiedenen Standards

- Elektrisches Verhalten der beschriebenen Standards

- Beschreibung der Datenregister in den Ein- und Ausgängen für DoubleData-Rate (DDR) Betrieb

- Beschreibung des Serialisierers bzw. des Deserialisierers

Im Artikel LVDS Signale anbinden hatte ich schon einmal auf dieses Dokument verwiesen.

Clocking Resources User Guide

UG382 – Spartan-6 FPGA Clocking Resources User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Beschreibung der verschiedenen Clock Ressourcen im Spartan-6 FPGA

- Techniken mit denen die Taktsignale gemanagt werden können

- Beschreibung der PLL (Phase Locked Loop)

Im Artikel Takterzeugung im FPGA hatte ich schon einmal auf dieses Dokument verwiesen.

Block RAM Resources User Guide

UG383 – Spartan-6 FPGA Block RAM Resources User Guide

Dieses Dokument beschäftigt ausführlich mit den Speicherblöcken (Block RAMs) im Spartan-6 FPGA. Es gibt eine technische Referenz, wofür diese Block RAMs genutzt werden können, wie damit effizient Daten gespeichert oder gepuffert werden können und was mit den Block RAMs noch für Funktionen ausgeführt werden können.

Configurable Logic Block User Guide

UG384 – Spartan-6 FPGA Configurable Logic Block User Guide

Dieses Dokument beschäftigt im Detail mit den konfigurierbaren Logic-Blöcken (Configurable Logic Block = CLB) im Spartan-6 FPGA. Es wird erklärt, was ein CLB ist, woraus er sich zusammensetzt und wie damit die verschiedenen Funktionen erzeugt werden können.

Außerdem wird eine Aufstellung geliefert, welche vorgefertigten CLB es im Spartan-6 gibt.

Packaging and Pinouts Product Specification

UG385 – Spartan-6 FPGA Packaging and Pinouts Product Specification

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Einführung in die Gehäuse des Spartan-6

- Tabelle mit den Pins

- Darstellung über die IO Signale und die Pins

- Mechanische Darstellung der Gehäuse

- Thermische Spezifikationen der Spartan-6 Gehäuse

- Darstellung der Markierung auf dem FPGA Gehäuse

- Anleitung zum Übergang von kleinen auf große Spartan-6 FPGAs

PCB Design and Pin Planning Guide

UG393 – Spartan-6 FPGA PCB Design and Pin Planning Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Grundlagen für die Technologie der Leiterplatte

- Energieversorgung für das FPGA inkl. detaillierter Übersicht, welche Kondensatoren verwendet werden sollten

- Übersicht über die IO Standards und z.B. über die Terminierung von Highspeed Signalen

- Grundlagen über das Leiterplattenmaterial und die Bedeutung für Highspeed Signale

- Eigenschaften von Highspeed Signalen

- Informationen zur Auswahl der IO Pins und der Taktsignale

- Design Regeln für die Footprints

Die 7 wichtigsten Userguides für Xilinx Artix 7

Nach der Liste der 6 wichtigsten Userguides für Xilinx Spartan 6 FPGAs folgt die Liste der 7 wichtigsten Userguides für den Xilinx Artix 7 FPGA.

SelectIO Resources User Guide

UG471 – 7 Series FPGAs SelectIO Resources User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Charakteristik und technische Werte der Ein- und Ausgänge

- Beschreibung der verschiedenen Standards

- Elektrisches Verhalten der beschriebenen Standards

- Beschreibung der Datenregister in den Ein- und Ausgängen für DoubleData-Rate (DDR) Betrieb

- Beschreibung des Serialisierers bzw. des Deserialisierers

Clocking Resources User Guide

UG472 – 7 Series FPGAs Clocking Resources User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Beschreibung der verschiedenen Clock Ressourcen im Artix 7 FPGA

- Techniken mit denen die Taktsignale gemanagt werden können

- Beschreibung der PLL (Phase Locked Loop)

- Informationen über das verteilen von Taktsignalen über mehrere Regionen im FPGA

Memory Resources User Guide

UG473 – 7 Series FPGAs Memory Resources User Guide

Dieses Dokument beschäftigt ausführlich mit den Speicherblöcken (Block RAMs) im Artix 7 FPGA. Es gibt eine technische Referenz, wofür diese Block RAMs genutzt werden können, wie damit effizient Daten gespeichert oder gepuffert werden können und was mit den Block RAMs noch für Funktionen ausgeführt werden können.

Weiterhin beschäftigt sich dieses Dokument mit den im Artix 7 integrierten FIFOs.

Configurable Logic Block User Guide

UG474 – 7 Series FPGAs Configurable Logic Block User Guide

Dieses Dokument beschäftigt im Detail mit den konfigurierbaren Logic-Blöcken (Configurable Logic Block = CLB) im Artix 7 FPGA. Es wird erklärt, was ein CLB ist, woraus er sich zusammensetzt und wie damit die verschiedenen Funktionen erzeugt werden können.

Außerdem wird eine Aufstellung geliefert, welche vorgefertigten CLB es im Artix 7 gibt.

Packaging and Pinout Product Specifications User Guide

UG475 – 7 Series FPGAs Packaging and Pinout Product Specifications User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Einführung in die Gehäuse des Artix 7

- Tabelle mit den Pins

- Darstellung über die IO Signale und die Pins

- Mechanische Darstellung der Gehäuse

- Thermische Spezifikationen der Artix 7 Gehäuse

- Darstellung der Markierung auf dem FPGA Gehäuse

- Anleitung zum Übergang von kleinen auf große Artix 7 FPGAs

GTP Transceivers User Guide

UG482 – 7 Series FPGAs GTP Transceivers User Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Einführung in die GTP Transceiver

- Beschreibung der Taktreferenz über eine eigene PLL

- Details über die Sender und Empfäger der GTP Transceiver

- Hinweise, wie die High-Speed Signale in der Elektronik angeschlossen werden sollten

PCB Design Guide

UG483 – 7 Series FPGAs PCB Design Guide

Dieses Dokument beschäftigt sich mit folgenden Themen:

- Grundlagen für die Technologie der Leiterplatte

- Energieversorgung für das FPGA inkl. detaillierter Übersicht, welche Kondensatoren verwendet werden sollten

- Übersicht über die IO Standards und z.B. über die Terminierung von Highspeed Signalen

- Grundlagen über das Leiterplattenmaterial und die Bedeutung für Highspeed Signale

- Eigenschaften von Highspeed Signalen

- Informationen zur Auswahl der IO Pins und der Taktsignale

- Design Regeln für die Footprints

Vergleich Xilinx Serie 7 FPGA

Übersicht

Xilinx FPGAs der Serie 7 gehören zum aktuellen Standard Programm von Xilinx. Sie werden in 28nm Technik gefertigt. Es gibt noch Untergruppen der Serie 7 FPGAs, die in kleineren Techniken gefertigt werden. Die UltraScale in 20nm und UltraScale+ in 16nm.

Artix 7

Der Artix 7 ist das „Einsteiger“ FPGA. Es verbraucht wenig Energie und kostet verhältnismäßig wenig. Die Preisespanne liegt bei ca. 20€ bis 300€.

Der Artix 7 kann als Nachfolger des Spartan 6 gesehen werden, der zur Low-Cost Serie von Xilinx gehört. Viele Eigenschaften, die auch schon der Spartan 6 hatte sind verbessert im Artix 7 wiederzufinden. Dazu gehören neben den seriellen High-Speed Tranceivern auch die SERDES oder die Taktmanager.

Kintex 7

Der Kintex 7 ist das „Mittelfeld“ FPGA. Hier liegt die Preisspanne etwas höher bei 120€ bis 5.720€ (wobei es sich hier im Distributor Einzelstück Preise handelt).

Wenn der Artix 7 nicht ausreichend ist (zum Beispiel bei den DSP48 Blöcken oder zu wenig internem Speicher), dann ist der Kintex 7 die richtige Wahl. Er liegt von der Ausstattung her zwischen Artix 7 und Virtex 7.

Virtex 7

Der Virtex 7 ist das „High-End“ FPGA, was man schnell an den Preisen für diese Bausteine merkt. Diese gehen von 2.300€ bis 35.500€ (wieder Einzelstück Preise vom Distributor).

In richtigen High-End Projekten mit viel I/O-Leistung (sowohl Pins, als auch Geschwindigkeit) bzw. auch mit vielen notwendigen Zellen, ist der Virtex 7 die richtige Wahl.

Untergruppen

Die beiden FPGAs Kintex 7 und Virtex 7 werden noch in drei Untergruppen unterteilt:

- die „normalen“ Bausteine mit 28nm

- UltraScale mit 20nm

- UltraScale+ mit 16nm

Hier steigen die Geschwindigkeiten auf Grund der kleineren Strukturen. Gleichzeitig sinkt auch die Energieaufnahme.

Zusammenfassung

Dieser Vergleich soll einen Überblick verschaffen, wofür man welches FPGA aus der Serie 7 einsetzten kann bzw. sollte. Mehr gibt es natürlich auch auf der Internetseite von Xilinx.

Takterzeugung im FPGA

Wie funktioniert im FPGA die Takterzeugung bzw. wie wird der Takt eines externen Generators richtig benutzt? Dieser Frage gehe ich am Beispiel des Xilinx Spartan 6 nach. Damit im FPGA ein sauberer Takt vorhanden ist, wird im Xilinx Spartan 6 (aber auch anderen Xilinx FPGAs) das Digital Clock Management (DCM) eingesetzt.

Codeschnipsel

-- Takt einbinden Inst_Systemtakt : Systemtakt port map( -- Clock in port CLK_IN1 => Clk_In_Buf, -- Clock out ports CLK_OUT1 => Clk_Int, CLK_OUT2 => Clk_100M_Int, CLK_OUT3 => Clk_8M_Int, -- Status and control signals RESET => dcm_reset, LOCKED => dcm_locked ) ;

Clocking Wizzard

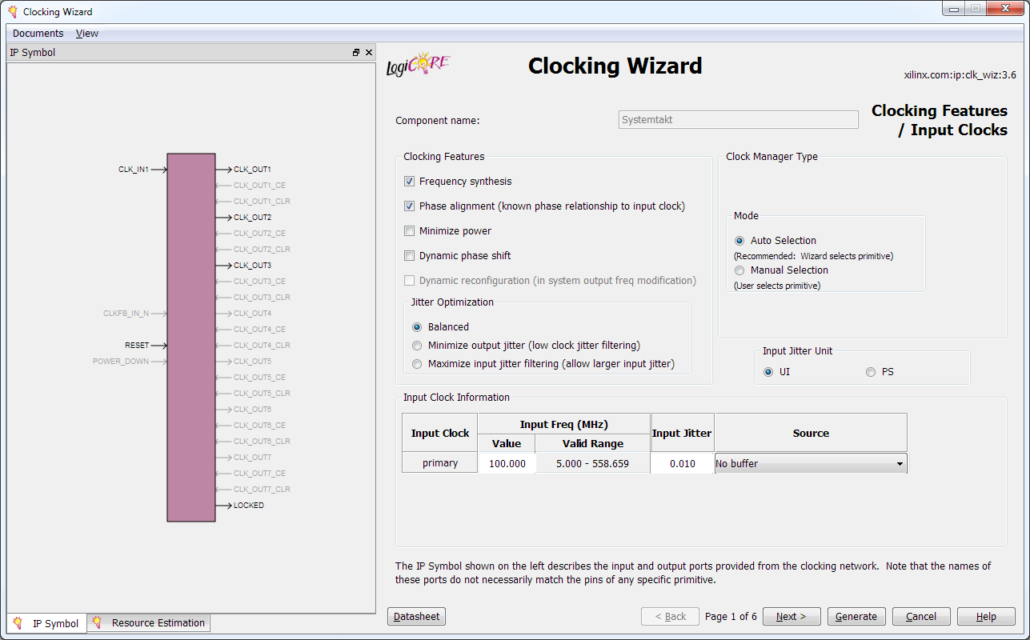

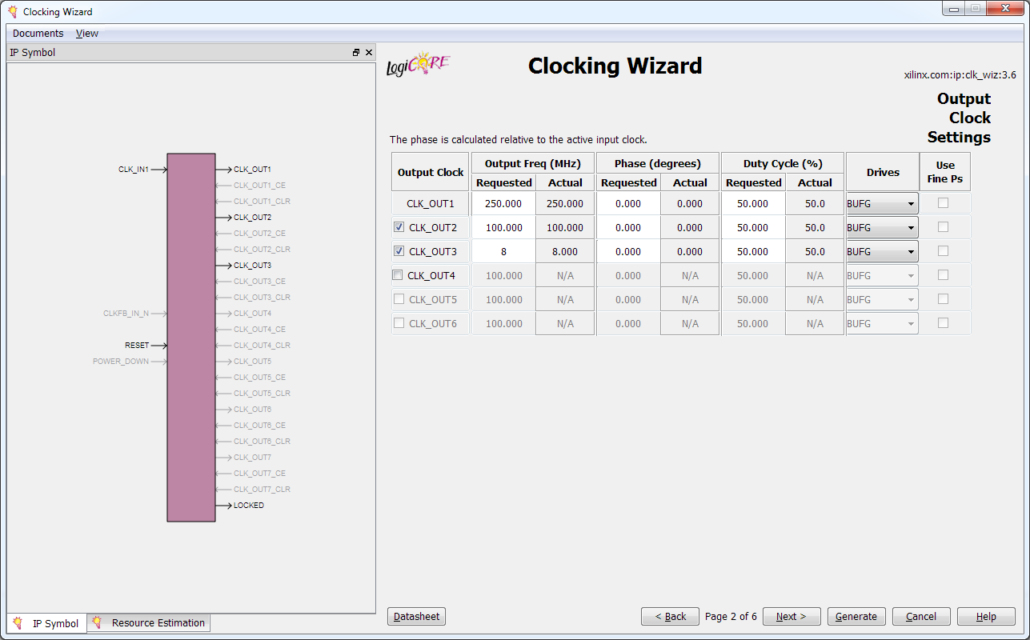

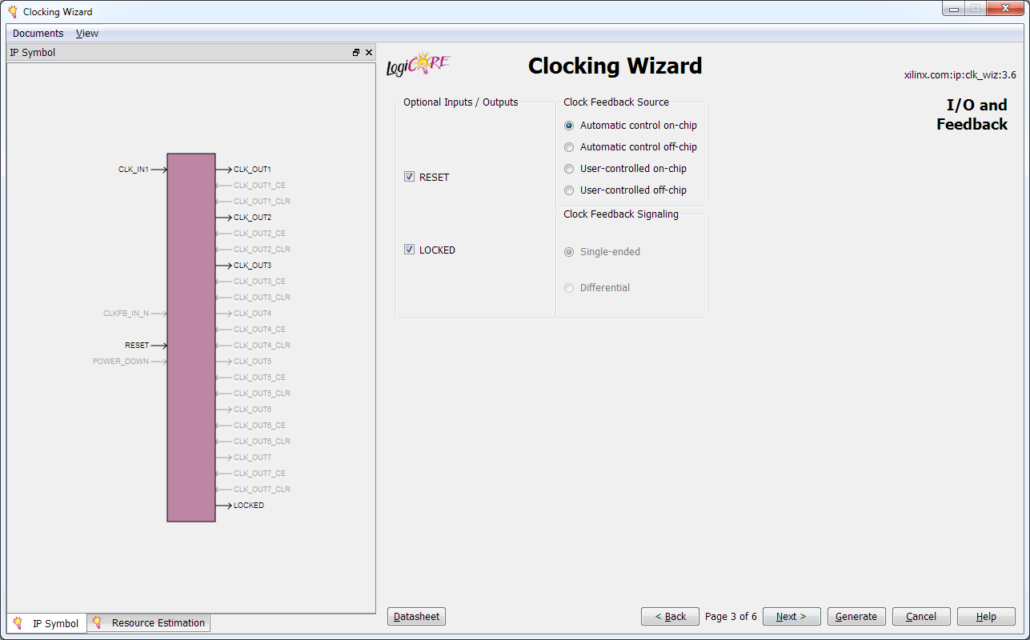

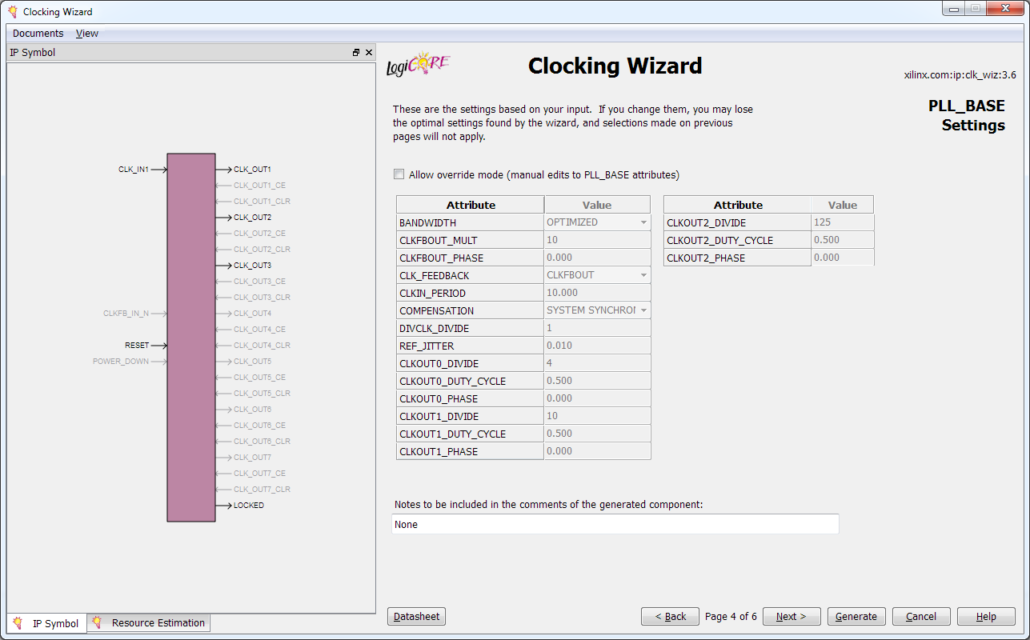

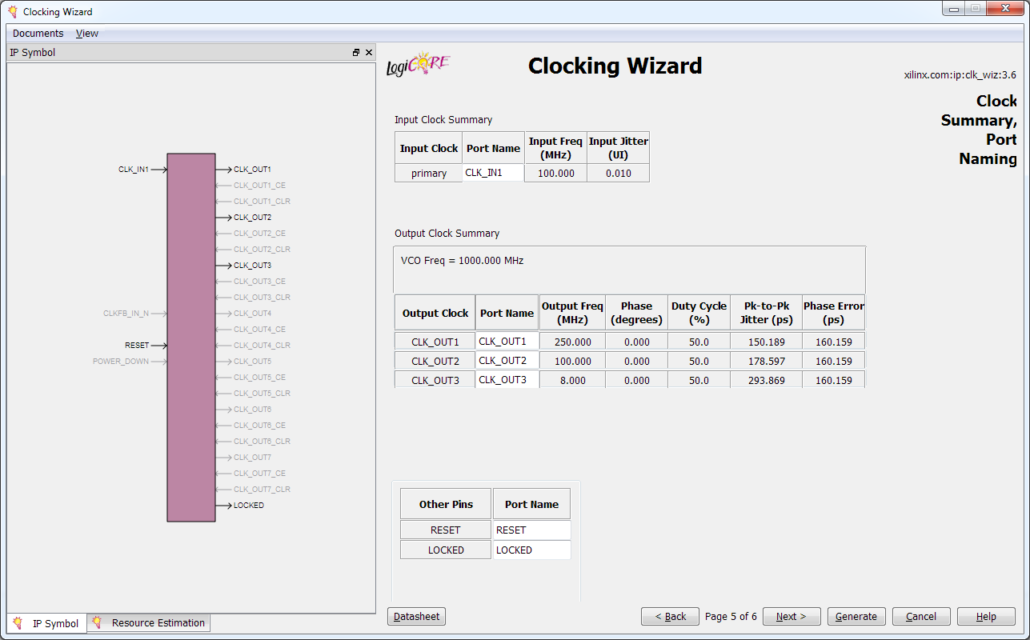

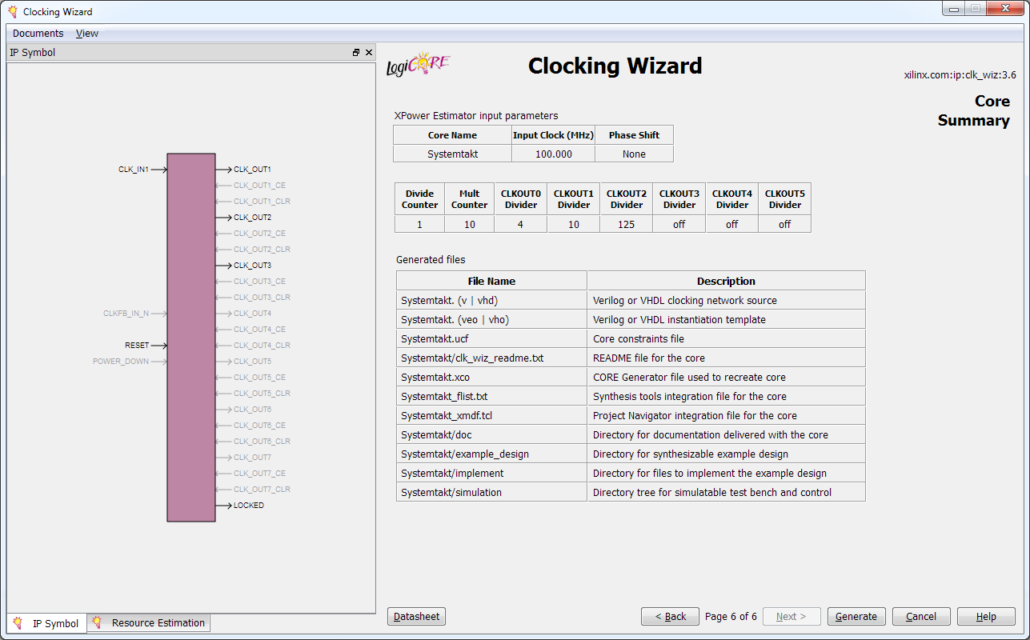

Der Codeschnipsel zeigt die Einbindung des IP-Cores von Xilinx. Nachfolgend ein paar Screenshots vom Xilinx LogiCore Clocking Wizzard:

Erklärung zu den Screenshots

Screenshot 1: Clocking Features and Input Clocks

In diesem Abschnitt wird die Eingangstaktfrequenz (im Beispiel 100MHz) und die Features der Komponente inkl. der Jitterperformance eingestellt.

Screenshot 2: Output Clock Settings

Auf der zweiten Seite werden nun die Anzahl der Ausgangstakte inkl. der Ausgangsfrequenzen eingestellt. Da nicht jede Frequenz erreicht werden kann, wird die zur Wunschfrequenz nächstliegende Frequenz angezeigt. Im Beispiel passen die Teiler zueinander.

Screenshot 3: I/O and Feedback

I/O and Feedback stellt zum einen ein, ob – und wenn ja – welche optionalen Ein- und Ausgänge zur Verfügung stehen sollen und wie der Feedbackpfad des Taktsignals gebildet werden soll. Im Beispiel möchte ich ein Reset-Signal (Eingang) und ein Locked-Signal (Ausgang) anschließen können. Der Feedbackpfad soll automatisch im FPGA gebildet werden.

Screenshot 4: PLL_BASE Settings

Hier kann man, wenn man möchte, die vom Wizzard erstellten Parameter manuell überschreiben. Dies sollte im Normalfall nicht notwendig sein.

Screenshot 5: Clock Summary, Port Naming

Die Namen der Ports (Takteingang und -ausgang und die optionalen I/Os) werden auf dieser Seite eingetragen. Weiterhin werden noch Informationen zu den erzeugen Taktsignalen ausgegeben.

Screenshot 6: Core Summary

Zum Schluss gibt es noch eine Zusammenfassung der Einstellungen und der Dateien, die erzeugt werden. Für die Einbindung in eine VHDL-Datei ist das Template mit der Dateiendung vho interessant. So erspart man sich unnötige Tipparbeit.

Abschluss

Weiterführende Informationen

Nachfolgend noch ein paar Verweise auf passende Dokumente:

- UG382 – Spartan-6 FPGA Clocking Resources User Guide [link]

- PG065 – LogiCORE IP Clocking Wizard 3.6 (ISE) / 4.2 (Vivado) Product Guide [link]

Zusammenfassung

FPGA und der synchrone Takt

Wie schafft es eigentlich ein FPGA, dass das synchrone Taktsignal an jedem Flip-Flip gleichzeitig ankommt? Und das bei Taktraten jenseits der 200MHz?

Taktverteilung

Die Frage ist bzw. die Fragen sind im Prinzip leicht zu beantworten: Man muss sich vorstellen, dass die Leitungslängen von der Quelle (z.B. ein internen Taktmanager) zu den Flip-Flops immer gleich lang ist. Damit wird schon die Forderung nach Synchronität erfüllt. Gleiche Leitungslängen im FPGA bedeuten auch gleiche Laufzeiten für das Taktsignal und die Flanken kommen alle zum selben Zeitpunkt am FPGA an.

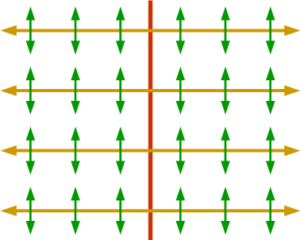

Doch wie genau macht ein FPGA das nun? Es gibt verschiedene Ansätze und einen (so verwendet beim Xilinx Spartan 6) stelle ich vor. Das Ersatzschaltbild ist dieses Mal eine Prinzipskizze des Taktnetzwerkes im FPGA. Zu sehen ist in der Mitte in rot die Vertikale Taktverteilung, in orange die horizontale Taktverteilung und in grün die lokalen Verteilung innerhalb der Regionen. Jedes Flip-Flop kann an unterschiedliche Taktnetzwerke angeschlossen werden. Teilweise werden bis zu 16 Netze im FPGA von der Quelle zu jedem (!) Flip-Flop geführt.

Diese Taktnetze sind nun so ausgelegt, dass diese mit hohen Signalfrequenzen umgehen können und diese – wie schon geschrieben – synchron an jedes Flip-Flop bringen.

Darstellung eines Verteilernetzes

Zusammenfassung

Zusammengefasst ist der Gedanke, synchrone Designs zu bekommen, relativ einfach. Man nehme nur gleich lange Leitung und fertig. Doch in der Praxis ist dies nicht trivial, sondern von jedem Hersteller von FPGAs sind das eine der vielen Know-Hows.

LVDS Signal anbinden

Bei der heutigen Geschwindigkeit von Signalen werden gerne differentielle Signale wie LVDS verwendet. LVDS bedeutet „Low Voltage Differential Signaling“, also differentielle Signal mit geringer Spannung. Der nachfolgende Codeschnipsel zeigt ein Beispiel in VHDL für einen LVDS-Eingang.

Codeschnipsel

— Eingangspuffer für Daten

Inst_Data_in_Buf : IBUFDS generic map ( DIFF_TERM => TRUE, -- Differential Termination IBUF_LOW_PWR => FALSE, -- Low power ( TRUE ) vs. performance ( FALSE ) setting for referenced I/O standards IOSTANDARD => "RSDS_33" ) -- IO-Standard RSDS_33 ( Low-Swing Differential ) port map ( O => Data_In, -- Clock buffer output I => Data_P, -- Diff_p clock buffer input ( connect directly to top-level port ) IB => Data_M -- Diff_n clock buffer input ( connect directly to top-level port ) ) ; -- Inst_Data_in_Buf

Erklärung

| Name | Wert | Erklärung |

|---|---|---|

| DIFF_TERM | TRUE | Der Eingang soll terminiert werden. |

| IBUF_LOW_PWR | FALSE | Der Eingang soll auf Persormance und nicht auf Energie optimiert werden |

| IOSTANDARD | RSDS_33 | Der Signalstandard RSDS_33 ist ähnelt LVDS, hat jedoch einen geringeren Hub. |

| Name | Wert | Erklärung |

|---|---|---|

| O | Data_In | Signalausgang in die FPGA-Logik |

| I | Data_P | Positiver Eingangs-Pin am FPGA (muss direkt mit Top-Levelport verbunden werden) |

| IF | Data_N | Negativer Eingangs-Pin am FPGA (muss direkt mit Top-Levelport verbunden werden) |

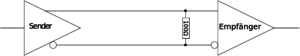

Ersatzschaltbild

Zusammenfassung

Das Primitiv IBUFDS kann innerhalb eines VHDL Quelltextes genutzt werden, um bei der Synthese genau vorzugeben, wie mit einem LVDS-Signal umgegangen werden soll. Für Takt-Netze gibt es noch eigenständige Primitivs, die ein Taktsignal dann in spezielle Netze routen kann.

Spartan 6 SERDES

Das FPGA Spartan 6 von der Firma Xilinx besitzt mehrere SerDes (Serialisierer und Deserialisierer). Damit lassen sich Datenströme von serielle in parallele Ströme umwandeln und andersrum. Es folgt ein Einblick in diese Funktion. Als Beispiel dient ein Eingangs-SerDes, der einen seriellen Datenstrom in einen parallelen Datenstrom aufteilt.

Codeschnipsel

Inst_ISerDes_Master : ISERDES2 generic map ( BITSLIP_ENABLE => TRUE, -- Enable Bitslip Functionality ( TRUE/FALSE ) DATA_RATE => "SDR", -- Data-rate ( SDR/DDR ) DATA_WIDTH => 8, -- Parallel data width selection ( 2-8 ) INTERFACE_TYPE => "RETIMED", -- NETWORKING, NETWORKING_PIPELINED or RETIMED SERDES_MODE => "MASTER" -- NONE, MASTER or SLAVE ) port map ( CFB0 => open, -- 1-bit Clock feed-through route output CFB1 => open, -- 1-bit Clock feed-through route output DFB => open, -- 1-bit Feed-through clock output FABRICOUT => open, -- 1-bit Unsynchrnonized data output INCDEC => incdec_data, -- 1-bit Phase detector output Q1 => Data_Out_int( 3 ), -- 1-bit Registered outputs to fabric Q2 => Data_Out_int( 2 ), -- 1-bit Registered outputs to fabric Q3 => Data_Out_int( 1 ), -- 1-bit Registered outputs to fabric Q4 => Data_Out_int( 0 ), -- 1-bit Registered outputs to fabric SHIFTOUT => cascade_m_s, -- 1-bit Cascade output signal for master/slave I/O VALID => valid_data, -- 1-bit Output status of the phase detector BITSLIP => bitslip, -- 1-bit Bitslip enable input CE0 => '1', -- 1-bit Clock enable input CLK0 => rx_clk_p, -- 1-bit I/O clock network input CLK1 => '0', -- 1-bit Secondary I/O clock network input CLKDIV => gclk, -- 1-bit FPGA logic domain clock input D => Data_Out_m, -- 1-bit Input data IOCE => rx_serdesstrobe, -- 1-bit Data strobe input RST => reset, -- 1-bit Asynchronous reset input SHIFTIN => cascade_s_m -- 1-bit Cascade input signal for master/slave I/O ) ; -- Inst_ISerDes_Master

Erklärung

Der obige Codeschnipsel beschreibt die Instanziierung eines Input SerDes im FPGA Spartan 6. Dies ließe sich auch über den CoreGenerator erzeugen. Hier soll jedoch auch die Möglichkeit gezeigt werden, was in VHDL möglich ist. Vorgaben hierzu liefert Xilinx mit, so dass man eine Grundstruktur direkt in seine VHDL-Datei einfügen kann.

Nachfolgend nun eine Übersicht über die genutzten Einstellungen:

| Name | Wert | Erklärung |

|---|---|---|

| BITSLIP_ENABLE | TRUE | Bitslip ermöglicht es, einzelne Bits zu überspringen, sofern es z.B. für das Timing notwendig ist. |

| DATA_RATE | SDR | Dieser Eingang wird im "Single Data Rate" Modus betrieben. |

| DATA_WIDTH | 8 | Der Ausgang soll 8 Bit Breite haben. |

| INTERFACE_TYPE | RETIMED | Es werden insgesamt 4 Flip-Flops in Reihe geschaltet, um eine optimale Abtaktung zu erreichen. |

| SERDES_MODE | MASTER | Dieser ISERDES ist der Master, somit gibt es noch einen Slave, der in Reihe geschaltet ist. |

Und die benutzen Ports:

| Name | Wert | Erklärung |

|---|---|---|

| INCDEC | incdec_data | Erkennung, ob zu früh oder zu spät abgetastet wurde. |

| Q1 | Data_Out_int( 3 ) | 4. Ausgangsbit |

| Q2 | Data_Out_int( 2 ) | 3. Ausgangsbit |

| Q3 | Data_Out_int( 1 ) | 2. Ausgangsbit |

| Q4 | Data_Out_int( 0 ) | 1. Ausgangsbit |

| SHIFTOUT | cascade_m_s | Kaskadenanschluss (Ausgang) |

| VALID | valid_data | Erkennung, ob INCDEC-Wert genutzt werden kann. |

| BITSLIP | bitslip | Steuereingang zum Überspringen von Bits. |

| CLK0 | rx_clk_p | Takt-Eingang des Signals |

| CLKDIV | gclk | Takt-Eingang der Ziel-Taktdomäne |

| D | Data_Out_m | Eingangsdaten |

| IOCE | rx_serdesstrobe | Signal, das die Übertragung in die FPGA-Logik steuert. |

| RST | reset | Asynchroner Reset-Eingang |

| SHIFTIN | cascade_s_m | Kaskadenanschluss (Eingang) |

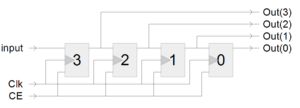

Im Endeffekt ist dieser SERDES ein Schieberegister, wie das Ersatzschaltbild verdeutlichen soll. Mit jedem Eingangstakt wird das Datenbit in der Kette weitergeschoben. Und nach vier Takten stehen alle 4 Bits am Ausgang zur Verfügung. Der SERDES unterstützt noch weitere Flip-Flop-Ketten, um z.B. den Übergang in die nächste Taktdomäne zu ermöglichen.

Ersatzschaltbild

Zusammenfassung

In heutigen Systemen werden immer mehr Daten seriell übertragen. Somit ist ein SERDES sehr häufig anzutreffen. Sei es als Interface für eine Kamera oder als HDMI-Eingang oder -Ausgang.

Weiterführend noch ein paar Literaturtipps:

Eine Beschreibung zu allen Einstellungen und Ports findet sich im Xilinx Userguide UG381 in Kapitel 3.

Weiterhin gibt es noch die Application Note XAPP1064, in der eine detaillierte Anleitung enthalten ist, wie z.B. auch ein Delay zur besseren Abtastung in der Mitte des Signals eingesetzt wird.

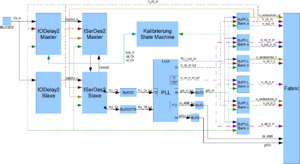

Automatische Verzögerung am Eingang

Im vorherigen Abschnitt hatte ich schon die automatische Verzögerung im Xilinx Spartan 6 erwähnt. Nun werde ich dieses Thema genauer betrachten und zeigen, dass diese Technik eigentlich ganz einfach ist. Es werden verschiedene Puffer benötigt und dazu noch eine Statemachine, die das Verzögern steuert.

Codeschnipsel

-- Statemachine zur kontinuierlichen Kalibrierung der Delays Proc_DelayCalc: process ( gclk_int, All_Locked ) begin -- Reset if All_Locked = '0' then state <= 0 ; enable <= '0' ; cal_Clk <= '0' ; rst_Clk <= '0' ; busyd <= '0' ; cnt <= ( others => '0' ) ; else if rising_edge( gclk_int ) then busyd <= busy_m ; if cnt( 5 ) = '1' then -- erst nach gewisser Zeit mit Kalibrierung beginnen enable <= '1' ; end if ; if cnt( 11 ) = '1' then -- Kalibrierung nach langer Zeit automatisch neu starten state <= 0 ; cal_Clk <= '0' ; rst_Clk <= '0' ; busyd <= '1' ; cnt <= ( others => '0' ) ; else cnt <= cnt + 1 ; -- eigentliche Statemachine: if state = 0 and enable = '1' and busyd = '0' then -- Wenn cnt( 5 ) = '1' dann weiter state <= 1 ; elsif state = 1 then -- cal auf high setzen cal_Clk <= '1' ; state <= 2 ; elsif state = 2 and busyd = '1' then -- auf Busy warten, dann cal auf low setzen cal_Clk <= '0' ; state <= 3 ; elsif state = 3 and busyd = '0' then -- auf Busy warten, dann rst auf high setzen rst_Clk <= '1' ; state <= 4 ; elsif state = 4 then -- auf low setzen rst_Clk <= '0' ; state <= 5 ; elsif state = 5 and busyd = '0' then -- auf Busy warten, dann in Warteschleife weitergehen state <= 6 ; elsif state = 6 then state <= 6 ; end if ; end if ; end if ; end if ; end process ;

Erklärung

Der Codeschnipsel zeigt „nur“ die Statemachine, die benötigt wird, um die möglichen Laufzeitverzögerungen auszugleichen. Damit werden Eingangspuffer nachgeregelt, damit die schnellen SERDES Signale optimal abgetastet werden können. Für eine optimale Abtastung muss die Flanke des Taktsignals in der Mitte des Datensignals liegen. Diese Mitte wird automatisch durch die Komponenten im Spartan 6 bestimmt.

Die Statemachine wartet nach dem Reset und nachdem alle PLLs gelockt sind mit Hilfe eines Zählers eine gewisse Zeit ab und startet dann die Kalibrierung. Diese erfolgt mit über die Signale cal_Clk und rst_Clk. Wenn die Kalibrierung abgeschlossen ist, geht die Statemachine in einen End-State. Da der Zähler jedoch weiterläuft, startet dieser nach einer weiteren längeren Wartezeit wieder die Kalibrierung. Damit werden Temperatureffekte ausgeglichen.

Das Ersatzschaltbild zeigt eine Übersicht über den kompletten Takt-Eingang und die verwendeten Elemente. Obwohl der Takt keine SERDES-Elemente benötigt, sind diese enthalten, um die Laufzeiten durch das SERDES zu messen.

Ersatzschaltbild

Zusammenfassung

Die automatische Kalibrierung der SERDES ist eine Technik, die Xilinx schon fast komplett in der Hardware implementiert hat. Nur die regelmäßige Durchführung der Kalibrierung muss durch die Statemachine ausgeführt werden.

HDMI am FPGA

HDMI ist immer wieder ein Thema für FPGAs. Gerade bei der schnellen und verzögerungsarmen Verarbeitung von Videosignalen ist ein FPGA perfekt geeignet. Da es bei dem Thema diverse Stolperstellen gibt, möchte ich eine erste Einführung in dieses Thema geben und in weiteren Blogposts zeigen, wie sich HDMI Signale an ein FPGA anbinden lassen.

Stolperstellen

Signalstandard

Der Standard für HDMI ist TMDS. Das Kürzel steht für Transition-Minimized Differential Signaling. Es ähnelt dem LVDS-Signal, doch gibt es hier eine Spezialität: Die Terminierung werden nicht zwischen den Signale mit 100Ω durchgeführt, sondern am Empfänger zwischen Signalleitung und Versorgungsspannung mit 50Ω.

Spannungspegel

Wichtig bei der Auslegung der Schaltungen ist, dass die I2C-Signale mit 5V Pegel betrieben werden.

Hotplugsignal

Der Sender erwartet vom Empfänger ein Hotplug-Signal, damit überhaupt eine Signalübertragung stattfindet.

Deserialisierung

HDMI setzt auf TMDS als Signalstandard und dieser hat einen 10-fach langsameren Takt und somit eine 10:1 Serialisierung bzw. 1:10 Deserialisierung.

Erklärung

Signalstandard

Im FPGA kann diese Terminierung im Normalfall nicht durchgeführt werden. Dadurch muss dieses Signal außerhalb des FPGAs terminiert werden. Es sind Widerstände von 50Ω gegen die 3,3V Spannung zu schalten. Der Sender hat Stromsenken gegen Masse verbaut.

Spannungspegel

Ein FPGA kann ein 5V Signal nicht verarbeiten, so dass diese I2C-Signale vorher durch einen Pegelwandler gewandelt werden müssen. Weiterhin hat auch das Hotplugsignal ein 5V Pegel.

Hotplugsignal

Das Hotplugsignal kann passiv über Widerstände oder aktiv über das FPGA-Signal gesteuert werden. Der Sender kann damit getriggert werden, die EDID Daten neu einzulesen.

Deserialisierung

Der Standard TMDS benutzt eine 8Bit/10Bit Wandlung, um durch Veränderung der Werte eine Minimierung der Signalübergänge zu erzeugen und damit die EMV-Abstrahlung zu verringern. Im FPGA ist demnach zuerst eine 1:10 Deserialisierung erforderlich und anschließend eine 10Bit/8Bit Wandlung.